【芯观点】2.5D/3D封装互联:苹果向左走,英特尔向右走

温馨提示:这篇文章已超过1162天没有更新,请注意相关的内容是否还可用!

集微网消息(文/思坦),巧或不巧地,3月初,因Apple Silicon分道扬镳的英特尔和苹果,“联手”将风光已久的先进封装,再次推上风口浪尖——

先有英特尔联合十大行业巨头官宣通用Chiplet高速互联标准UCIe,后有苹果发布史上最强M1 Ultra芯片,最大卖点落于封装架构UltraFusion。

从本质上来说,UCIe是生态层面的统一接口IP标准,UltraFusion是物理层面的键合技术,但从目标来看,两者均瞄准于Chiplet“乐高化”的最大痛点——D2D(die to die)互联。

苹果向左:键合技术硬核推进

如果说Chiplet是大楼,那么接口IP就类似于楼梯间,键合技术则是楼梯,两者结合负责每一楼层(即die)的互联。在技术路线尚未统一的当下,各方在实现die to die互联技术的尝试各有不同。UCIe联盟中,苹果和英伟达的缺席,或许正代表来了这种分歧。

作为台积电InFO先进封装解决方案最著名一战的客户方,苹果将其先进封装技术的锚点选在键合技术上,并不难理解。根据集微网从厦门云天获得的一份调研报告显示,这个细节被苹果以“采用硅中介层进行互联”一笔带过的UltraFusion封装技术,其中实现的突破,足以带来互联技术的内部地震。

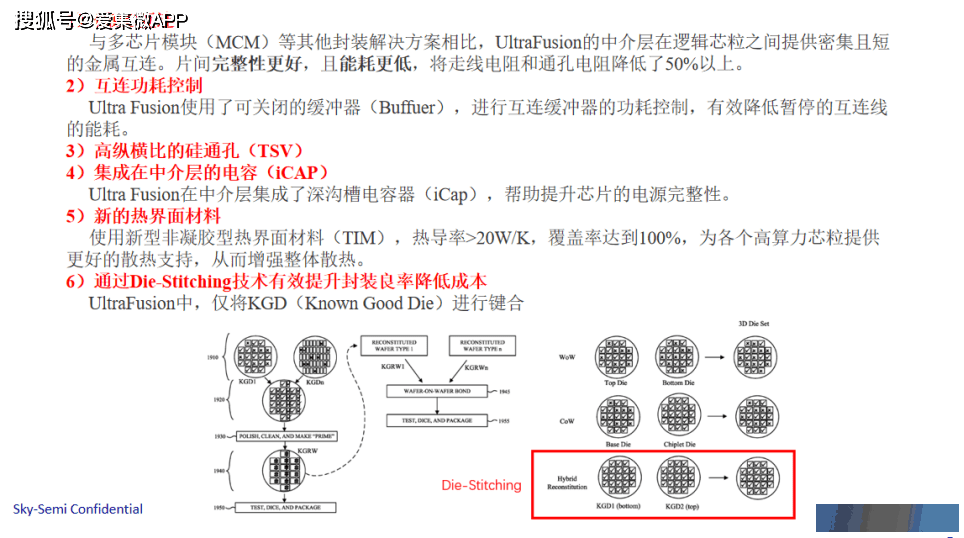

与此前业内猜测的无凸点键合技术不同,UltraFusion仍然建立在微凸点的设计上,但主要做出了下图所示的六大改进,而其中帮助苹果成为业内首个实现GPU裸片互联的最关键在于中介层实现的高密度互联以及Die-Stitching(裸片缝合)技术。

图源:厦门云天

GPU裸片互联难点在于消耗的内部带宽过高,UltraFusion基于台积电第五代CoWoS-S技术,两个裸片通过中介层布线传输超过10000个信号,连接密度是现有技术的两倍,提供的2.5TB/s超高处理器间带宽(是其他互联技术带宽的4倍多)有效解决了带宽问题。

更大的光罩尺寸也为两颗GPU裸片腾出了空间,据了解,台积电第5代CoWoS-S技术达到了大至三个全光罩尺寸(~2500mm2)的水平,作为对比,英伟达4年前集成了HBM的GPU,光罩尺寸仅为815mm2,台积电为此采用了裸片缝合技术。

目前尚不清楚在UltraFusion上来自苹果的研发占比,鉴于英伟达、AMD预计也将于今年依托于台积电技术推最新一代GPU,抢先实现GPU裸片互联的苹果必然有所依仗。虽然苹果于去年才获得其第一个先进封装专利,但其与台积电早已携手在这一领域进行研发,对终极技术的追求也比想象的更远。

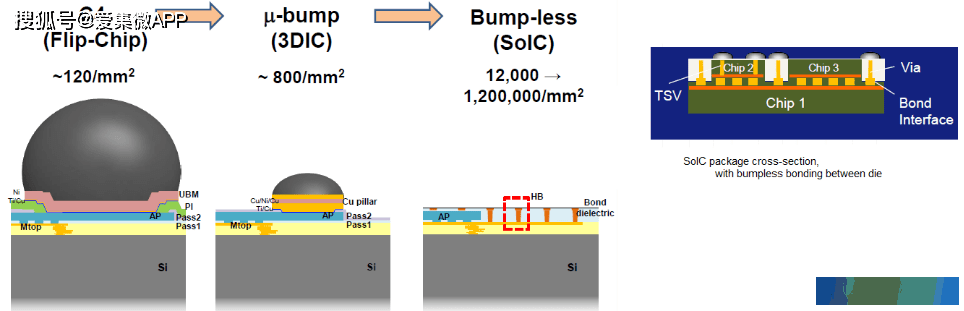

无凸点键合是苹果目前仍在追求的技术突破方向。厦门云天董事长于大全教授对笔者表示,苹果很早就开始与台积电共同研究无凸点键合方法,主要特征是不再使用后道集成所用的凸点,转而直接将裸片类似于“铜对铜”地堆叠到一起。这种方法除了没有“凸点间距”这一紧箍咒外,还能大大降低热阻。

从C4凸点到无凸点;图源:台积电

另外耐人寻味的是,今年以来,苹果官网已发布多条与先进封装相关的职位,其中一个名为“先进封装开发工程师”的职位,要求应聘者有至少10年的晶圆厂集成工作经验,其中至少5年的先进封装工作经验,具有BEoL工艺、RDL、细间距微凸点、混合键合、TSV等裸片互连工艺集成经验。

英特尔向右:接口IP广发英雄帖

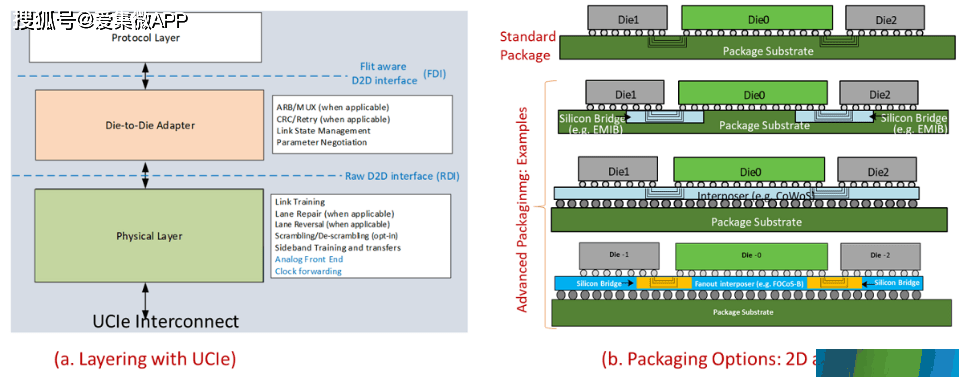

与苹果键合技术的“独孤求败”相比,英特尔成立UCIe联盟,更像是武林盟主广发英雄帖,通过将接口IP标准化,进一步消除障碍,使来自不同制程工艺、不同设计公司的裸片更顺畅地互联,也使得更多无法承担接口IP研发的中小企业,加入到chiplet的浪潮。

据集微网此前报道(《【芯调查】Chiplet“乐高化“开启 UCIe联盟要打造芯片的DIY时代》https://laoyaoba.com/n/809720),业界资深人士何凌(化名)曾对此解释称,过去,一个Chiplet组合中,裸片无论是通过硅桥还是基板连接,都需要制定新的传输协议,“UCIe的出现相当于交通规则实现统一,打破了不同工艺和晶圆厂之间的界限。”

英特尔在一份声明中表示:“UCIe创建的芯片生态系统是为可互操作的chiplet创建统一标准的关键一步,这将最终允许下一代技术创新。”功利一些的看法是,英特尔正花费数十亿美元建立采用3D封装制造芯片的工厂,更多公司加入意味着更多的需求和更高的利用率。

UCIe可提供的die to die互联方式的选择;图源:英特尔

这也符合英特尔近期“扩大生态朋友圈”的大转向,其于2月初宣布启动一项新的10亿美元基金,优先投资于加快代工客户芯片上市的技术,包括IP、软件工具、创新芯片架构和先进封装技术,重点关注关键的战略性行业变化,例如利用开放芯片平台实现模块化产品。

这种策略将对其在这一领域持保护主义的竞争对手造成冲击,特别是苹果和英伟达都未出现在联盟名单里。英特尔加速计算系统和图形事业部副总裁兼总经理Raja Koduri在上个月的投资者大会上表示:“我们认为,从长远来看,封闭的方式无法获得如此巨大的机会。”

有业内分析认为,苹果“靠边站”的原因很直接——其5nm SoC技术已超越了所有竞争对手,未来也不太可能加入类似联盟。另外笔者也猜测,与英特尔需要更大的需求来分担成本不同,苹果仅为自己的产品提供芯片,可以完全将成本压力转嫁给消费者,因而更能够专注于烧钱的键合技术上。

但这并不代表苹果对接口IP不屑一顾。需要强调的是,苹果尚未向外界公开过其与接口IP有关的开发情况,而这事实上这对于裸片互联来说几乎是无法绕过的技术,AMD有Infinity Structure,英伟达有NVLink,苹果有的是什么?这或许更是隐藏在UltraFusion之后,苹果真正的秘密武器?

此外,根据IPnest预测,2021年-2025年,接口IP将以22.4%的年增长率增至25亿美元,其中以太网以及D2D(die to die,裸片对裸片)增速最高达29%,这将是IP供应商在chiplet上看到的最大商机,这就不难解释为何与英伟达剪不断理还乱的Arm会出现在UCIe联盟名单中。

降低chiplet门槛以提升2.5D/3D封装需求、增加市场参与者以给与保守的竞争对手、联手接口IP供应商扩大朋友圈……从可能达到的效果来看,英特尔以接口IP突破D2D封装互联技术,图谋远大,类似于举生态之力进行技术推进,选择了与苹果的硬核推进全然不同的路线。

写在最后

对于2.5D/3D封装互联,键合技术和接口IP缺一不可,鉴于自身在行业中的不同环节,选择不同路径突破的苹果和英特尔,谁将在先进封装领域掌握更大的主动权,目前来看还很难说。

然而,一个很容易被忽视的重点在于,无论是Ultra Fusion和UCIe联盟,台积电都在其中扮演了主要或次要的地位。这个耐人寻味的重点,或将是2.5D/3D封装互联战场,真正的X因素。(校对/隐德莱希)

九七分享吧所有文章来源于网络收集整理,如有侵权请联系QQ2387153712删除,如果这篇文章对你有帮助或者还不错的请给小编点个小赞(◠‿◠),小编每天整理文章不容易(ಥ_ಥ)!!!

还没有评论,来说两句吧...